Cortex-M3(32位处理器内核)

温馨提示:这篇文章已超过532天没有更新,请注意相关的内容是否还可用!

Cortex-M3

32位处理器内核

Cortex-M3是一个32位的核,在传统的单片机领域中,有一些不同于通用32位CPU应用的要求。谭军举例说,在工控领域,用户要求具有更快的中断速度,Cortex-M3采用了Tail-Chaining中断技术,完全基于硬件进行中断处理,最多可减少12个时钟周期数,在实际应用中可减少70%中断。

单片机的另外一个特点是调试工具非常便宜,不象ARM的仿真器动辄几千上万。针对这个特点,Cortex-M3采用了新型的单线调试(SingleWire)技术,专门拿出一个引脚来做调试,从而节约了大笔的调试工具费用。同时,Cortex-M3中还集成了大部分存储器控制器,这样工程师可以直接在MCU外连接Flash,降低了设计难度和应用障碍。

| 外文名 | Cortex-M3 |

| 定义 | 32位处理器内核 |

| 结构 | 哈佛结构,独立指令、数据总线 |

| 内部数据路径 | 32位 |

| 寄存器 | 32位 |

| 存储器接口 | 32位 |

概述

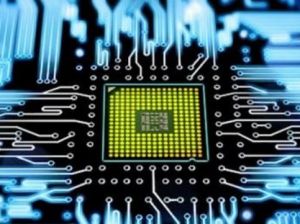

Cortex-M3是一个32位处理器内核。内部的数据路径是32位的,寄存器是32位的,存储器接口也是32位的。CM3采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。这样一来数据访问不再占用指令总线,从而提升了性能。为实现这个特性,CM3内部含有好几条总线接口,每条都为自己的应用场合优化过,并且它们可以并行工作。但是另一方面,指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)。换句话说,不是因为有两条总线,可寻址空间就变成8GB了。

比较复杂的应用可能需要更多的存储系统功能,为此CM3提供一个可选的MPU,而且在需要的情况下也可以使用外部的cache。另外在CM3中,Both小端模式和大端模式都是支持的。CM3内部还附赠了好多调试组件,用于在硬件水平上支持调试操作,如指令断点,数据观察点等。另外,为支持更高级的调试,还有其它可选组件,包括指令跟踪和多种类型的调试接口。

内核架构

ARMCortex-M3采用哈佛结构,并选择了适合于微控制器应用的三级流水线,但增加了分支预测功能。现代处理器大多采用指令预取和流水线技术,以提高处理器的指令执行速度。流水线处理器在正常执行指令时,如果碰到分支(跳转)指令,由于指令执行的顺序可能会发生变化,指令预取队列和流水线中的部分指令就可能作废,而需要从新的地址重新取指、执行,这样就会使流水线“断流”,处理器性能因此而受到影响。

特别是现代C语言程序,经编译器优化生成的目标代码中,分支指令所占的比例可达10-20%,对流水线处理器的影响会的更大。为此,现代高性能流水线处理器中一般都加入了分支预测部件,就是在处理器从存储器预取指令时,当遇到分支(跳转)指令时,能自动预测跳转是否会发生,再从预测的方向进行取指,从而提供给流水线连续的指令流,流水线就可以不断地执行有效指令,保证了其性能的发挥。

ARMCortex-M3内核的预取部件具有分支预测功能,可以预取分支目标地址的指令,使分支延迟减少到一个时钟周期。针对业界对ARM处理器中断响应的问题,Cortex-M3首次在内核上集成了嵌套向量中断控制器(NVIC)。Cortex-M3的中断延迟只有12个时钟周期(ARM7需要24-42个周期);Cortex-M3还使用尾链技术,使得背靠背(back-to-back)中断的响应只需要6个时钟周期(ARM7需要大于30个周期)。Cortex-M3采用了基于栈的异常模式,使得芯片初始化的封装更为简单。

Cortex-M3加入了类似于8位处理器的内核低功耗模式,支持3种功耗管理模式:通过一条指令立即睡眠;异常/中断退出时睡眠;深度睡眠。使整个芯片的功耗控制更为有效。

产品概述

单片机的另外一个特点是调试工具非常便宜,不象ARM的仿真器动辄几千上万。针对这个特点,Cortex-M3采用了新型的单线调试(SingleWire)技术,专门拿出一个引脚来做调试,从而节约了大笔的调试工具费用。同时,Cortex-M3中还集成了大部分存储器控制器,这样工程师可以直接在MCU外连接Flash,降低了设计难度和应用障碍。

ARMCortex-M3处理器结合了多种突破性技术,令芯片供应商提供超低费用的芯片,仅33000门的内核性能可达1.2DMIPS/MHz。该处理器还集成了许多紧耦合系统外设,令系统能满足下一代产品的控制需求。ARM公司希望Cortex-M3核的推出,能帮助单片机厂商。

Cortex的优势应该在于低功耗、低成本、高性能3者(或2者)的结合。Cortex如果能做到合理的低功耗(肯定要比Arm7&Arm9要低,但不大可能比430、PIC、AVR低)+合理的高性能(10~50MIPS是比较可能出现的范围)+适当的低成本(1~5$应该不会奇怪)。简单的低成本不大可能比典型的8位MCU低。对于已经有8位MCU的厂商来说,比如Philips、Atmel、Freescale、Microchip还有ST和SiloconLab,不大可能用Cortex来打自己的8位MCU。对于没有8位MCU的厂商来说,当然是另外一回事,但他们在国内进行推广的实力在短期内还不够。

对于已经有32位ARM的厂商来说,比如Philips、Atmel、ST,又不大可能用Cortex来打自己的Arm7/9,对他们来说,比较合理的定位把Cortex与Arm7/9错开,即<40MIPS的性能+低于Arm7的价格,当然功耗也会更低些;当然这样做的结果很可能是,断了16位MCU的后路。对于仍然在推广16位MCU的厂商来说,比如Freescal、Microchip,处境比较尴尬,因为Cortex基本上可以完全替代16位MCU。

所以,未来的1~2年,来自新厂商的Cortex比较值得期待-包括国内的供应商;对于已有32位ARM的厂商,情况比较有趣;对于16位MCU的厂商,反应比较有意思。

主要控制

LM3S101是一个高性能的ARM®Cortex?-M3v7M架构的微控制器,适用于成本敏感的应用。它支持完全兼容Thumb的Thumb-2-only指令集,具有硬件除法和单周期的乘法器。集成的嵌套式的中断控制器(NVIC)提供确定性的中断处理。目标应包括:工厂自动化及控制,工业控制动力设备,以及楼宇家庭自动化。

参考资料

1.ARM推出针对MCU领域的Cortex-M3·21ic电子网