edk(嵌入式系统的工具)

温馨提示:这篇文章已超过541天没有更新,请注意相关的内容是否还可用!

edk

嵌入式系统的工具

EDK=Embedded Development Kit,嵌入式开发套件。 EDK是xilinx公司开发嵌入式系统的工具。比起xilinx的ISE,二者不同在于,如果仅仅是使用xilinx的fpga做逻辑设计,只需要ISE开发环境。但是如果要使用powerpc或者microblaze处理器,从硬件到软件设计的整个嵌入式系统设计,就需要EDK。

| 中文名 | edk |

| 外文名 | Embedded Development Kit |

| 属于 | 嵌入式开发套件 |

| 公司 | xilinx公司 |

EDK基本介绍

嵌入式系统经历了从 单片计算机、 工业控制计算机、集中 分布式控制系统,发展到嵌入式的平台的几个阶段:从独立单机使用发展到联网设备;从以模拟电路为主发展到以数字电路为主、数/模混合型,进而进入全数字时代。总的来说, 嵌入式系统向着更高性能、更小体积、更低功耗、更廉价、无处不在的方向发展。 嵌入式系统的设计和实现朝着基于芯片,特别是片上可编程系统(SOPC)的方向发展。

嵌入式开发套件(EDK)是用于设计嵌入式可编程系统的全面解决方案。该套件包括嵌入式 软件工具(Platform Studio)以及嵌入式IBM PowerPC硬件处理器核和/或Xilinx MicroBlaze软处理器核进行Xilinx平台FPGA设计时所需的技术文档和IP。注意,这里的嵌入式 软件工具指用来产生、编辑、编译、链接、加载和调试高级 编程语言(通常是C或C++)代码的工具,以便在处理器引擎上执行。

由于 嵌入式系统涉及了软件和硬件的开发以及两者的综合设计,因此其开发是较为复杂的。Xilinx为了简化基于FPGA的 嵌入式开发流程,提供了功能强大、操作简单的工具集:集成 软件环境——ISE;嵌入式开发套件——EDK。(注释:ISE 是Xilinx 公司FPGA 逻辑设计的基础。在这个环境中,设计者可以进行约束文件的编写,时序分析,逻辑布局布线以及器件 编程等。)

EDK自带了许多工具和IP,可以用来设计完整的 嵌入式处理器系统,主要包括Xilinx 平台工作室XPS和 软件开发套件SDK。需要注意的是:只有安装了ISE软件,才能正常运行EDK,且二者的版本要一致。

EDK的组成模块有:

1.Xilinx 平台工作室(Xilinx Platform Studio,XPS)

XPS 是用来设计 嵌入式处理器系统硬件部分的开发环境或GUI,是系统设计者构建 Xilinx 嵌入式系统时必用的工具套件。在XPS中,可以完成 嵌入式系统架构的创建、 软件代码的编写、设计的编译以及FPGA芯片的 硬件配置。

2.软件开发套件(Software Development Kit,SDK)

SDK是集成的 开发环境,基于Eclipse。它支持C/C++,用于 嵌入式软件应用的开发和验证。

3.其它EDK部分

EDK还包括其它的一些部分,如:用于Xilinx 嵌入式处理器的硬IP;用于嵌入式软件开发的驱动和库;在MicroBlaze和PowerPC处理器上用于C/C++软件开发的GNU编译器和调试器;有关文档以及一些工程样例等。

Xilinx的 嵌入式开发套件EDK带有许多的工具和IP,可以用来设计完整的 嵌入式处理器系统,并在Xilinx FPGA芯片上运行。EDK中包含了开发硬件和软件所必须的全部工具,可以很方便的添加系统自带的IP核和用户自定义的IP核,可以通过调用ISE等其他工具实现布局布线,时序优化等等。可以调用GDB对应用程序进行板上调试及虚拟平台调试。

EDK设计的实现流程

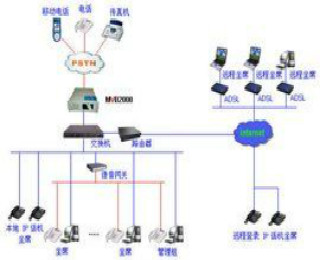

基于EDK的开发流程

一个完整的嵌入式设计流程包括硬件设计和调试、软件设计与调试,各个步骤相对独立但又相辅相成。由于嵌入式应用场合多样,且软、硬件都可裁剪,因此并不是每个设

计都要完成所有的步骤。图中为基于EDK 的嵌入式设计的简化流程图。

通常,ISE FPGA 开发软件在后台运行,XPS 工具调用ISE 软件提供的功能。XPS 主要用来嵌入式处理器硬件系统的开发。微处理器、外围设备以及这些组件之间的连接问题,另外还有它们各自的属性设置都在XPS 里进行。简单的软件开发可以在XPS 里完成,而对于更复杂的应用开发和调试,Xilinx 则推荐使用SDK 工具。硬件平台的功能验证可以通过硬件描述语言HDL 仿真器完成。XPS 提供了行为级、结构级以及定时精确级等三种类型的仿真。验证过程结构由XPS 自动产生,其中包括了仿真的HDL 文件。设计者只需要输入时钟时序、重配置信息以及一些应用代码即可。仿真细节将在下面的内容中进行相关讲述。完成设计后,在XPS 中将FPGA 比特流和可执行可链接格式文件下载,就可以进行目标器件的配置。

完整的EDK 开发流程如右图 所示,其主要步骤有:

1. 创建硬件平台:利用XPS 的板级开发包向导(BSB Wizard)快速构建设计的硬件平台,是EDK 设计的第一步。

2. 添加IP Core 以及用户定制外设:在XPS 中添加所需的IP Core,对于XPS 库中缺少的模块,需要用户自行设计。同样,XPS 提供了建立用户自定义外设的向导,可简化该过程。

3. 生成仿真文件并测试硬件系统:生成硬件系统的仿真文件,可选择行为级、结构级以及时序级仿真,利用ModelSim等工具测试系统,特别是用户自定义的外设;如果测试失败,需要返回上一步修改。

4. 生成硬件比特流:生成硬件网表和比特流文件,这个步骤类似于传统FPGA 设计的综合、布局布线、生成编程文件这3 个操作。

5. 开发软件系统:针对软件需求编写硬件代码,确定软件的操作系统、库、外设驱动等属性,针对每个应用软件工程,设置编译器、优化级别、使用的连接文件等信息。等设置完成后,编译生成.elf 格式的可执行代码。

6. 合并软、硬件比特流:编译软件后,需要将软、硬件可执行文件合并在一起,生成最终的二进制比特文件。

7. 下载:使用JTAG编程电缆或编程器将更新后的最终比特流烧写到 FPGA、PROM、FLASH以及CF 卡。

8. 在线调试:可利用XMD工具或ChipScope 工具调试,通过JTAG编程电缆在线调试,下载可执行软件代码、控制执行,并监控相关信息。

EDK设计比特文件的组成

如前所述,最终下载到FPGA 的嵌入式比特流文件是软、硬件比特流合并在一起的,详细的组成部分如右图

所示。硬件部分比特流包括MHS 文件、用户自定义HDL 代码,二者经过综合实现后,产生.ngc 网表,生成硬件系统的比特流文件;软件系统包括 MSS 文件、用户.c/cpp/asm文件,通过GCC 编译器,生成目标文件.obj,再经过连接合成软件系统的比特流文件;最后通过Data2MEM过程,将软、硬件比特流合成完整系统比特流文件,通过JTAG链路下载到FPGA 芯片中。

实验——添加自定义IP

安装时候需要版本搭配,如ISE8.1搭配EDK8.1。首先,说说使用EDK加入用户设计的IP。

1、启动XPS(xilinx platform studio),生成一个processor system,其中可以选择处理器,硬IP(powerpc)或软IP( microblaze),以及可选的IP(BRAM、UART)等。如果这个阶段拿不定不要什么IP,以后添加删除都可以。

2、启动Create and Import Peripheral Wizard,创建IPIF,选择需要的属性,如是否包括FIFO、DMA等,系统会自动创建HDL文档模板,用户只需要添加 用户程序部分。同coreconnect总线连接部分不用用户操心。

3、使用ISE的Project Navigator,打开第二步生成的.npl文件,添加入自己的代码,在ISE里进行编译。

4、如果需要,进行BFM(总线 功能模型)仿真

5、若在第三步里,用户对接口有修改,需要重新启用Create and Import Peripheral Wizard,来生成EDK接口(.pao/.mpd文件)

6、使用XPS - Add/Edit Core Dialog,添加用户IP到第一步的工程中

7、使用XPS生成IP driver。

8、编译、下载bit文件到 开发板。

参考资料

1.基于MicroBlaze 的嵌入式系统设计·华强电子网